# Design of femtoampere circuits with low leakage, part one

S,E Nickols, Diablo Mountain Research LLC – July 28, 2021

Circuits that carry femtoamperes (10<sup>-15</sup> amperes) of current have many subtleties that you wouldn't normally consider in the design and layout of conventional circuitry. If you overlook these subtleties, the circuit loses low-end resolution and exhibits drift due to the components, materials, and circuit layout. Knowing the circuit's limitations and leakages and providing ways to minimize or eliminate them will lead to improved circuit performance.

The world below a picoampere (10<sup>-12</sup> amperes) is unique and plays by a different set of rules. In this world, even the mechanical parts of the circuit can become parts of the electrical circuit. Designing for operation at subpicoamp and femtoamp levels requires special techniques and compromises that normal current levels don't generally require. Unfamiliarity with or neglecting these precautions can result in endless headaches for designers. Electrical engineers will find themselves playing double roles as mechanical engineers.

This three-part article guides you through the tricky and unconventional design techniques you need to create successful low-current circuits. This first part defines and describes the designs that carry these low currents. It explains the problems that arise when you design these circuits and examines the application of shielding and guarding methods. Part two will examine how your component selection affects the performance of your low-leakage circuits and discuss how noise creeps into low-leakage designs. Part three will provide detailed PCB-design techniques and show a real-world example of a low-leakage design. It will also describe how to verify the performance of your low-leakage-design techniques.

### Low-current applications

To put things into perspective, 1A equals 6,241,500,000,000,000,000, or  $6.24^{18}$  electrons/sec; 1 pA, or  $10^{-12}$ A, equals 6.24 million electrons/sec; and 1 fA, or  $10^{-15}$ A, equals 6240 electrons/sec. In the subpicoamp world, there are three common enemies: current leakages, noise sources, and

stray capacitance. A good low-current design must minimize the effects of these common enemies and strike a balance between optimal performance and product manufacturability. You will need special techniques and materials that may be incompatible with conventional production flows.

These high-impedance circuits often go directly into an amplifier input with no parallel-resistive connections. Examples of these circuits include pH probes, gas-sensor amplifiers, medical sensors, sample-and-hold circuits, and three-amplifier instrumentation amplifiers. The circuits can have input impedances into the teraohm range. A transimpedance amplifier, or current-to-voltage converter, is often used at these low current levels. You see this circuit configuration in noninverting amplifiers, photodetector amplifiers, current-to-voltage converters, and photomultiplier circuits. The amplifier's inverting input node and its feedback elements are critical nodes. The current leakage in this node determines the ultimate accuracy of the device.

Higher-current circuits, such as low-frequency filters and logarithmic amplifiers, also benefit from low-leakage-design techniques. They will have extended dynamic range, with improved low-end accuracy and lower drift than nonoptimized designs.

### **Causes of disturbance**

### **Causes of disturbance**

Dirty PCB traces can cause leakage at low currents. The dirt between the traces or across insulating materials—not the trace or wire itself—causes the leakage, serving as a conductive medium between two conductors. Dry dirt in itself may not cause a problem. A combination of dirt with moisture, salts, and oil, however, becomes conductive. The concept here is simple: Keep things clean.

Moisture is the instigator of most leakage problems. When moisture combines with environmental salts and other contaminants, its conductivity increases. Insulation, PCBs, and other hydroscopic materials absorb the moisture, decreasing the electrical resistance of the materials and leading to increased leakage between the conductors.

Contamination between conductors can also create a galvanic reaction in the presence of the right combination of materials and moisture. Moist and salty dirt between a copper trace and a zinc-plated screw or an aluminum case will generate a current between the materials. This current is detrimental to your measurement and causes corrosion of the materials. Because the moisture level varies over the course of the day, season, and geographical location, it creates a moving baseline leakage that is difficult to remove. These leakages change hourly, weekly, or yearly, depending on the environment and the season.

The particles and moisture in air as it moves over a conductor generate a small charge, so you should protect the input circuit from moving air currents. Make sure that fan-cooling airflow does not blow directly over sensitive nodes. Airflow can also cause dust and moisture to accumulate on the conductors and components.

You must take into account the properties of insulating materials in your design. These materials come into direct contact with low-level signals, usually through the connectors, the supports, or the PCB. In the electronics industry, the most common insulators are fiberglass, glass, ceramic,

PVC (polyvinyl chloride), epoxy, and Teflon. Each material has its own weaknesses and strengths. Dry air is a good insulator. Keeping conductors in the air can provide the lowest-leakage results. Air does have a low breakdown voltage, however, which limits this technique in high-voltage applications. PTFE (polytetrafluoroethylene) and FEP (fluorinated-ethylene propylene), more commonly known as Teflon, have the best leakage and high-voltage characteristics of common insulating materials, but they are expensive, soft, and difficult to machine. Teflon PCBs are expensive because of the material and the extra steps the fabrication process requires.

Ceramic, although a good insulator, tends to be piezoelectric. Ceramic self-generates charge when it is subjected to stress or impact. It also readily absorbs moisture if it is not sealed or glazed. Although glass is a good insulator, it displays some of the piezoelectric properties of ceramics. IC packages use a molded glass-epoxy compound that allows for currents lower than 1 fA. Epoxy is an excellent, low-cost insulator; however, it is hydroscopic and can absorb moisture over time. Many components, connectors, and wire insulation use PVC, which can generate charge if flexed or rubbed against another conductor, just as combing your hair can generate current. For this reason, PVC insulation in and around the input circuit should be avoided.

It might seem logical to build the ultimate low-leakage layout entirely on a slab of Teflon. This can be a bad idea, however. Because Teflon is a good insulator, any charge deposited on its surface will slowly dissipate. If a sensitive node is nearby, the accumulated charge will lead to slow settling or drift. A better approach is to cover a large surface area with a guarded conductive plane. Although this approach seems counterintuitive to the desire for low leakage, you should minimize the use of insulators. Insulation must provide isolation, but using too much of it provides a surface to accumulate extra charge.

For low-voltage circuits, an aluminum standoff topped with a small piece of Teflon insulation works better and is less expensive than using an entire standoff made of Teflon. If the circuit will be handling high voltages, you need a Teflon standoff for its better insulating properties. For ac circuits, the narrow insulator has higher stray capacitance that may cause other problems. As in all analog design, you must consider many trade-offs. PCBs have a large influence on low-leakage design because the PCB material is in intimate contact with all of the circuit nodes.

The performance of your circuit is only as good as the performance of the PCB material. As with RF circuits that operate at gigahertz speeds, you should consider the PCB as an active component. Most PCBs' material characteristics and development focus on high-frequency RF designs. Manufacturers gear PCB specifications toward circuits that operate at these speeds. They give a nod to low-current requirements by specifying a volume resistivity. The manufacturer's specifications are for the fresh laminate material before processing—not the finished product. That product comprises a sandwich of laminates, bonding glues, fillers, solder masks, and silk-screen that make up a PCB.

The most common PCB material is FR4 (flame-resistant 4), which comprises epoxy-impregnated fiberglass cloth. Manufacturers compress this epoxy under high pressure to form a solid board. FR4 has good electrical properties, but it is not the most desirable material for low-current circuits. You can improve the performance of FR4 using special layout and circuit techniques.

When performance is more important than cost, you can use exotic Teflon or ceramic hybrids, such as Rogers Corp's Duroid hybrid substrate materials, targeting use in microwave and ultrahigh-speed digital circuits. The materials' excellent controlled dielectric properties can result in two- to three-times-lower stray capacitance and leakage than those of FR4, but at a cost two- to five-times higher.

The boards also require special PCB-fabrication processes and etching, which some PCB-fabrication houses may be unable to accommodate. The Rogers soft, bendable 3003 material, which is ceramic-reinforced PTFE, requires backing for mechanical stability. Rogers 5880, a glass-reinforced PTFE, gives the best low current and stray capacitance, but it is brittle and cracks easily. It is possible to create a hybrid board, with advanced materials for the critical layers and FR4 for noncritical layers and mechanical stability. This approach is expensive and requires using an advanced board house, however.

Use caution with solder-mask placement. Although solder masks generally help reduce moisture infiltration into the PCB material, surface-charge problems might arise with large areas of Teflon. A better approach uses a bare-copper guard-plane area around sensitive nodes. To prevent oxidation, either solder-level or plate the bare-copper guard area with gold or tin.

Shield, guard, enclose

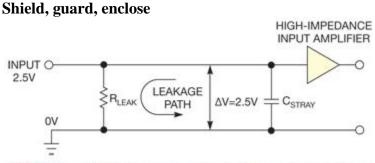

You wire a metallic shield, case, or enclosure to a ground or a common potential. At high impedances, however, these shields create problems with stray capacitance and leakages. Examine, for example, a circuit with a 2.5V input voltage and with 2.5V across the stray-capacitance and leakage paths (**Figure 1**). The 2.5V across the leakage resistance creates a leakage current, and the 2.5V source voltage charges or discharges the stray capacitance, which takes some time to get through the high source impedance and affects the measurement's settling time.

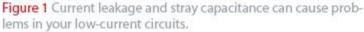

Figure 2 Adding a guard ring between the input node and ground will reduce leakage and capacitive-loading effects.

Guards are important in subpicoamp designs because they can cancel the input-leakage currents and most of the fixture capacitance. You drive the guard to a potential equal to the input-signal level. You apply a buffered output derived from the measurement amplifier. This guard acts as a subshield, surrounding and protecting the input-signal lines. External leakages now flow into the low-impedance guard instead of the input traces (**Figure 2**). This approach yields only a few millivolts of potential difference instead of 2.5V across and smaller current flows through leakage resistor  $R_{LEAK}$  and stray-capacitance capacitor  $C_{STRAY}$ . As a bonus, guards also reduce the input capacitance through a bootstrapping effect. Performed correctly, this approach can cancel out fixture and cable capacitance. Unfortunately, you cannot cancel out the amplifier's input-stage capacitance.

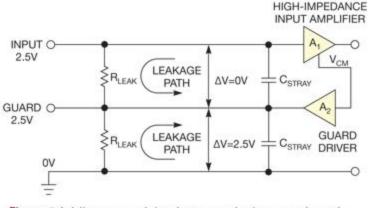

Locate the input traces and all of the sensitive feedback components on your PCB within the perimeter of the thick copper-guard traces (**Figure 3**). Then, remove the solder mask from this area to reduce surface charges. Buffer amplifier  $A_2$  drives the guard ring. In the inverting and transimpedance designs, you drive the guard to the same potential as the noninverting input's node and feed the potential on the noninverting pin to the guard buffer. The noninverting node is low-impedance, and the buffer does not affect the circuit's operation. The guard should cover the entire input section, the inverting node, and the feedback resistor. Extend it as far into the sensor circuit as possible without affecting sensor operation.

Figure 3 The thick copper trace on this PCB acts as a guard ring. The goldplated traces prevent corrosion. Remove the solder mask in the guarded area to reduce leakage.

When designing in the noninverting mode, drive the guard to the same potential as the inverting input node through a buffer. This node follows the input signal through the feedback action of the amplifier. Take care that the capacitance of the buffer's input does not cause peaking due to capacitive loading of the inverting node. The guard-driver amplifier should be unity-gain-capable and protected from short circuits and external overvoltages. The bandwidth of the buffer should be slightly wider than the main circuit's bandwidth to reduce phase-lag errors. Avoid a peaking response in the guard buffer to prevent system instability. A grounded shield protects the circuit from external noise and EMI by shunting the noise to ground. Because the grounded shield generally does not follow the input voltage, it does not cancel the capacitance caused by the guard.

In the previous examples, you buffer the guard line from a circuit node using a separate amplifier, providing a low impedance to drive the shields and coaxial-cable guards. If you need to guard a small location, you can derive a local guard from the opposite input terminal. Keep in mind that the local guard also adds capacitance to the node to which it connects. This capacitance can lead to peaking in noninverting-amplifier configurations. If the opposite node is high-impedance, the guard can introduce external noise into the summing node unless you shield the guard itself. Do not use an unbuffered guard to drive external circuitry. Use it only for the immediate area surrounding the device.

Keep in mind that the guard is not ground, and ground is generally not a guard. The guard lines should not carry any currents other than the leakages, and you should treat them as signal lines. For effective designs, use guards and grounds together. The guard surrounds the input trace, and the grounded shields protect the guards from external interference. When you lay out a PCB, place a guard plane or guard traces below the sensitive traces. Be careful not to break up the power or ground layer too much. Surround the input circuit in a guarded cocoon using metallic shields on visible component sides and guard traces on layers below the sensitive nodes.

You should enclose your low-current circuits in a sealed environment. If possible, include a desiccant pack to absorb any traces of moisture. The wiring and control shaft entry and exit points should be airtight. You can use triaxial cables and connectors for low-current measurements. The cable contains both an outer grounding shield and an inner guard shield around the center conductor, extending the guard out to the measurement point. Commercial test equipment often uses Trompeter 70-series triaxial BNCs. Agilent prefers the three-lug style, while Keithley prefers the two-lug style.

Part 2 examines how your component selection affects the performance of your low-leakage circuits and discusses how noise creeps into low-leakage designs.

### Reference

1. Low Level Measurements Handbook, Sixth Edition, Keithley Instruments, 2004.

# **Design femtoampere circuits with low leakage - Part 2: Component selection**

S,E Nickols, Diablo Mountain Research LLC – July 29, 2021

Part one of this article defines and describes the designs that carry these low currents, explains the problems that arise when you design these circuits, and examines the application of shielding and guarding methods. In Part 2, we examine how your component selection affects the performance of your low-leakage circuits and discuss how noise creeps into low-leakage designs.

### Component Effects

### Resistors

High-impedance circuits, by nature, involve the use of high value resistors. Values range from hundreds of kilo-ohms up into the hundreds of Megohms and even as high as tens of Teraohms.

Figure 1. Glass Enclosed Multi-Gigohm Resistors

Beyond the normal resistor errors that we expect, the familiar tolerance and temperature coefficient (tempco), there are other errors that are important in these circuits.

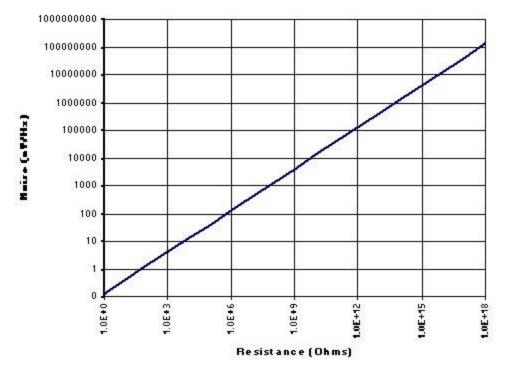

Large resistors generate lots of noise. Mr. Johnson's beloved thermal equation<sup>1</sup> produces very large numbers when solving for these very large resistance values. A 10Meg resistor generates  $2.4\mu$ Vp-p of noise in just a 1Hz bandwidth. A 1Gigohm resistor generates  $24\mu$ Vp-p noise in just a 1Hz BW.

### Theoretical Resistor Noise @ 25°C

Figure 2. Resistor Thermal Noise

A quick way to get the rough nV/Hz RMS resistor noise at room temperature  $(25^{\circ}C)$  is to multiply the square of the resistance by 0.13 (or 0.128299).

Resistor noise in nVrtHz = 0.13 \* sqrt(R) (Multiply RMS by 6 to get Vpp).

In most cases, you will find the noise is greater than the expected signal level. It is important to limit the measurement bandwidth to just what is required. Every extra Hz of bandwidth is just adding more noise.

The exotic materials used in the construction of the high-value resistors can also add additional noise, which can add to the theoretical noise. It is not unusual to find the noise slightly higher than what was calculated for the resistance value.

Resistors can also have a significant parallel capacitance. The typical ¼ watt resistor can have 0.15pF to 0.5pF in parallel with the resistor. When dealing with high impedances, every pF counts, especially with the high value feedback networks.

One trick to reduce the series capacitance is to use several resistors in series instead of one resistor. This way the capacitive strays are placed in series.

Figure 3. Resistors in series to reduce capacitance

If one 10Meg resistor is 0.2pF, then two 5Meg resistors in series are 0.1pF, five 2Meg resistors are 0.04pF, and ten 1Meg resistors are 0.02pF. More than five is getting into diminishing returns. The resistors should be soldered end-to-end and all placed above the board for best results. Two or three surface mount resistors can be mounted vertically on the same pad.

High value resistors can also have a voltage coefficient, where the value of the resistance changes as the voltage across the resistor increases. This is most apparent at high voltages (>100V), and is usually not a big problem for small signal feedback resistors since the voltages across them are very low or zero.

Some of the resistors, particularly multi-Gigohm surface mount types, are made out of exotic substrate materials, and may require silver solder or other special soldering precautions. Examine the resistor datasheet very carefully, and read the manufacturers application notes.

The bodies of high value resistors should not be touched, and should be handled only carefully by the leads to prevent getting body oils on the resistor body surfaces. These resistors may also have a thin protective silicone coating to seal out moisture that must be protected. Gloves are recommended if handling by the resistor body is necessary. Resistors with values in the thousands of gigohms are generally encased in a glass body to reduce leakage and protect the element. Again, read the datasheet carefully for any warnings or special handling and cleaning instructions.

### Capacitance

There are two types of capacitors: intentional and unintentional. "Intentional" capacitors are the ones you purposely place in your circuit, and "unintentional" are the ones you did not place there but are naturally hanging off every node of your circuit. These unintentional capacitors are known as "strays", as any conductor facing another conductor is a capacitor.

Because of the ultra high impedances generally involved with low current measurements (>Gohm), the effects of device and stray circuit capacitance are very prevalent and cannot be ignored. A few pF of stray capacitance, which normally one would not even think about in a "normal" circuit, can become a big nuisance in high impedance circuits. Time constants in the multi-gigohm and picofarad world can range into the seconds, even minutes.

Component and stray capacitance will usually dictate the ultimate bandwidth of a circuit, and not the bandwidth of the amplifier. So minimizing stray capacitance is critical if any bandwidth is required.

### Capacitor "Soakage", or Dielectric Absorption

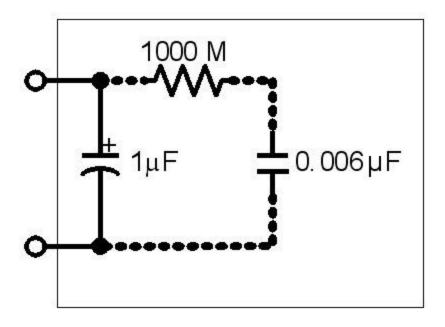

Capacitor "Soakage", or Dielectric Absorption is a capacitors seeming ability to "remember" what voltage it was previously charged to after being discharged.

One can think of the soakage model as a second capacitor with a very large series resistance in parallel with the main capacitor.

Figure 4. Model of Capacitor Soakage

Simply shorting the main 1uF capacitor does not completely discharge the "parallel" capacitor completely because of the series resistance. The parallel capacitor then re-charges the main capacitor slowly through the series resistance. The result is the main capacitors open-circuit voltage slowly creeps up to a value close to the original charge voltage.

Because of the high impedances generally used in low current circuits, this effect can be a noticeable part of a measurement, particularly in sample and hold, integration capacitors, and even the capacitance of some insulation materials.

The type and quality of dielectric or insulation determines the amount of soakage. Teflon and Poly capacitors are very good, whereas tantalum, ceramic and most electrolytic capacitors can be poor. Even other materials, such as PC boards, connectors and insulators can have these absorption effects. Bob Pease wrote an article<sup>2</sup> in which he tested several types of capacitors for leakage. As expected, Teflon and various Poly capacitors topped the list of lowest absorption, and tantalum, mica and ceramic had the highest.

Nodes should be grounded or kept at minimal potentials when idle to minimize dielectric absorption. Capacitors should be shorted with a small value resister when idle. Avoid keeping large voltages on measurement nodes for extended periods and do not let integrators "rail" for long periods.

## Design femtoampere circuits with low leakage - Part 3: Low-current design techniques

S,E Nickols, Diablo Mountain Research LLC – July 30, 2021

Part 1 of this article defines and describes the designs that carry these low currents, explains the problems that arise when you design these circuits, and examines the application of shielding and guarding methods. Part 2 examines how your component selection affects the performance of your low-leakage circuits and discuss how noise creeps into low-leakage designs.

### **Low-Current Design Techniques**

### a. Leave things up-in-the-air

For proper operation of critical sub-picoamp circuits, some "unconventional" construction techniques may be required.

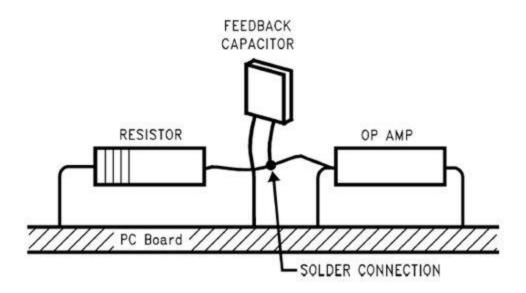

The classic low-current technique is the "up-in-the-air" wiring technique, where leads of the components in the critical path or circuit node are soldered together above the board. These component leads and traces do not come in contact with the board, so the influences of the PC board are effectively eliminated.

Teflon standoff terminals can be used to support large components or heavily populated nodes. The area below the components should be a solid, bare guard plane.

Figure 1: Up-In-The-Air wiring

This technique provides the lowest leakage, lowest stray capacitance and best overall low current performance, but requires hand assembly and is not easy to do in mass production or limited space areas. The entire circuit does not have to be placed above the board, only the critical nodes. In Figure 1 above, the inverting node of the circuit, which includes the input signal, feedback resistor and capacitor, are all soldered directly to the bent-up leg of the Op Amp inverting terminal.

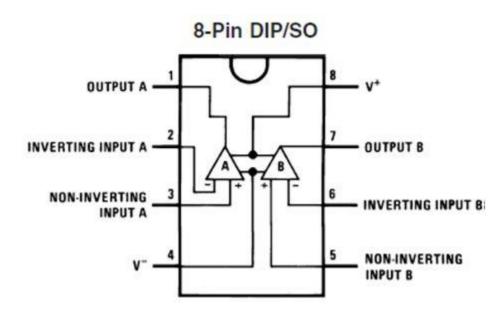

### b. Use Second Channel of a Dual

Here is a little tip: If you are designing a circuit that uses the non-inverting configuration, use the second ("B") channel of a dual as your main amplifier.

### Figure 2: Standard Dual Op-Amp Pinout

In the standard dual pinout, the "B" non-inverting input is farther away from the negative power supply pin, and is also "guarded" to the north by the inverting pin, and the input is on the corner of the package for easy connection to the source. There is also more room to run a guard trace between V- and the "B" non-inverting pin. The "A" channel amplifier can be used as a guard driver.

The single pinout suffers the same issue as the "A" channel, where the non-inverting input is close to the power supply. With the exception of a tiny single option, it may be more advantageous to use a dual version if both the single and dual are in the same 8-pin package.

### c. Small packages may not be so good...

Figure 3: Small Package comparison (top row) SOT-23, SC-70, TSSOP-14, (bottom row) SOIC-8 and MSOP-8

Packages with tighter lead pitches tend to have higher leakages. This is mainly because of the tight lead spacing and closer proximity to the supply lines and other pins. The board's resistivity per square stays the same, but moving the pads closer reduces the distance, decreasing the resistivity.

Also, the tighter pitch can trap dirt quicker and it is more difficult to properly clean at these tight pitches. This is one of the few times a SOIC-8 would be better than a MSOP-8 if space is not at a premium. The old DIP package is still the best package in this regard. For these same reasons, the SOT-23 single is preferred to the SC-70 single.

### **Design and Layout Suggestions**

Here are some general suggestions to keep in mind for your own design.

Guard traces should surround all the input stages. Guard PC board on the inner-layers and the bottom layer, too. The output does not need to be guarded, as it is low impedance, but it should be shielded from the input stages.

There is a tradeoff between guard spacing and input capacitance. A wider gap between the guard and input trace reduces the input capacitance.

Minimize the input surface area to reduce the effects of stray capacitance and ionization strikes. Since I-R drop is not a big issue at picoamp signal levels, and the speeds are generally low, use as narrow a trace width as possible to reduce strays. Use minimum size SMT pads to maximize space between pads.

Secure all loose wires. Sensitive high-impedance circuits can "see" a wire moving ( $\Delta C$ ). Within the guarded area, jumper or interconnection wires should be bare (no insulation, tinned solid copper preferable).

PC Board areas with solder mask removed should be enclosed within a sealed guard or shield to protect from moisture and dust.

Only use as much Teflon or other insulation around conductors as needed. Guard the rest of the area. Beware of spacing required for high voltage.

Watch out for plastic and tape use on the board. Use ESD conductive tape.

Ceramic capacitors are piezoelectric – mechanical vibrations and noises will create charge across the capacitor. Be careful when using ceramic caps in the input, integration, feedback or biasing networks.

The entire enclosure should be environmentally sealed, and desiccant packs should be used when humidity may be an issue. These packs should be easy to replace by the user or the metrology lab as part of a regular calibration or field service.

Minimize board flexing and stresses. Use multiple board mounting points or supports and do not support external user controls and connectors only by the board.

As was mentioned in the beginning of the article, designing successful circuits at sub-picoamp levels requires different design practices compared to "conventional" circuits. By following the simple advice above, a high level of first-time success can be achieved.

### **Design Challenge**

The author was tasked with improving the performance of an evaluation board for the LMP7721 low-input-bias-current CMOS operational amplifier. The board needed to showcase the near-femtoamp input current performance of the device, while still using standard low-cost FR4 board and conventional surface-mount components. The board also had to support multiple circuit configurations.

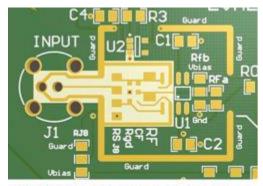

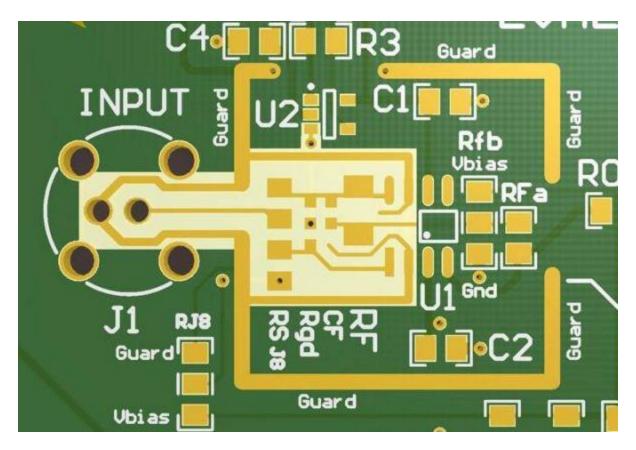

Figure 4: LMP7721 Evaluation Board

The first step was minimizing the input surface area. This reduces the stray input capacitance, makes the input easier to guard, minimizes the effects of electrostatic coupling and ionization strikes.

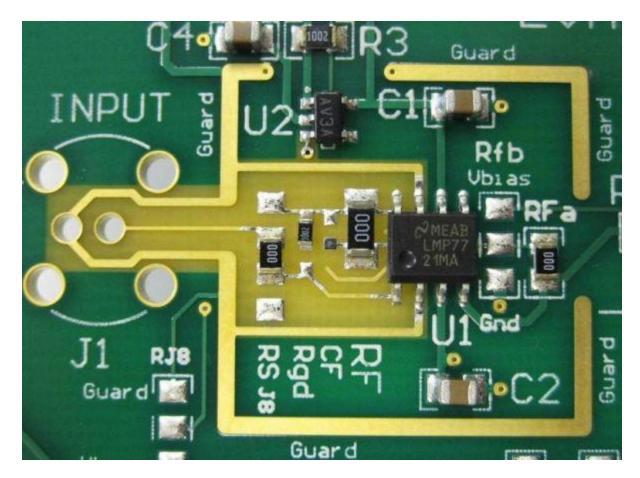

Figure 5: Input Section of board showing guarded area

An extensive buffered guarding system was added surrounding the input circuit. Wide traces were added to the perimeter to allow the attachment of an optional metallic shield surrounding the entire circuit.

The input traces and all the sensitive feedback components are located within the perimeter of the smaller guard box. The larger outer bare copper square box is for soldering on a metal guard shield to cover the entire input circuit.

The LMP7721 has a unique pinout that separates the input pins (pins 1 and 8) from the power and output pins with guard pins (pins 2 and 7). These pins are connected to the guard to provide guarding all the way down to the lead frame level.

The solder mask has also been removed from this area to reduce charge accumulation.

Figure 6: Multi-Use Resistor Pads

To minimize input capacitance, and to reduce the physical surface area of the input, the input traces are very thin and the resistor pads serve double duty as jumpers.

The layout is designed to accommodate inverting, non-inverting and buffer configurations by changing a few resistors and jumper resistors (the "buffer" configuration is shown in the photo).

Normally, each resistor, and even the unused resistor options, would have their own pads. This would leave several unconnected pads "floating" unused.

Instead, the pads were laid out so that placing the resistor in the appropriate position completed the circuit and selected the configuration.

The result is a very tight, compact layout with minimum exposed input conductors. Of course, a dedicated circuit would be much smaller and compact.

### Properly cleaning the board

Proper cleaning of the board is ultra-critical to provide the expected sub-picoamp performance.

Properly cleaning the board and components takes a few extra steps over conventional methods. Leftover flux residue, moisture and cleaning residues will severely degrade the low current performance.

The use of "no wash" spray flux is not recommended for the final cleaning. Water soluble fluxes can still leave a film behind.

The board should be re-cleaned after any rework to components within the guarded areas.

The board should be washed with isopropyl alcohol or methanol, making sure all remaining traces of moisture are removed from the board. Areas between the component leads should be scrubbed and areas under surface mount devices thoroughly flushed.

Figure 7: Cleaning board with Acid Brush

In the picture above, the board is scrubbed using an acid brush that has had the long bristles cut to a short length to increase the bristle stiffness. This is to allow for better scrubbing in between the device pins.

After a "standard" cleaning, the recommended extended cleaning procedure would be:

- Remove all traces of moisture otherwise it will react with the alcohol and leave white powdery deposits behind.

- Flood board with alcohol (80% or better).

- Scrub between device leads, connectors and around components with stiff brush.

- Flood with alcohol again to flush out debris and blow excess off with compressed air. Also flush and blow under SMT devices. Don't forget about the bottom of the board!

- Quickly dab dry and then wipe dry with clean towelette.

• Bake board to drive out remaining moisture.

After cleaning, only handle the board by the edges and do not touch anything inside the guard area. Avoid breathing on the board, as saline moisture in the breath can severely degrade performance. If any changes are made to the components within the guarded area, the cleaning procedure should be repeated.

The board should be stored in a sealed container or bag, preferably with a desiccant pack.

### Verifying the board's performance

### Verifying the board's performance

After assembling and cleaning the board, the performance of the board has to be measured. A simple test was devised to check the performance.

For the inverting or transimpedance amplifier, the leakage is measured simply by disconnecting the source and observing the baseline "zero" level. Any levels above the theoretical baseline level are most likely due to leakage. However, because these circuits contain large resistors, resolving femtoamps can be difficult due to the noise.

The non-inverting configuration has the highest input impedance and is the most sensitive to leakages. For this reason, the non-inverting buffer configuration was chosen to test the board performance.

To test the non-inverting input, an open-circuit "float" test was used. The leakage current is integrated across the input capacitance. From the resulting drift rate and the known input capacitance value, the leakage current can be calculated.

The non-inverting input "float" test is fairly simple. The input is temporarily grounded with a wire, and then opened by quickly removing the grounding wire from the input. The input is then allowed to "float" unconnected as the output voltage is measured at regular time intervals to calculate the current.

The equipment required for the test is fairly simple, only requiring a DMM and a stopwatch or similar interval logging setup. A digital scope can also be used for this function if one is available.

### The Setup

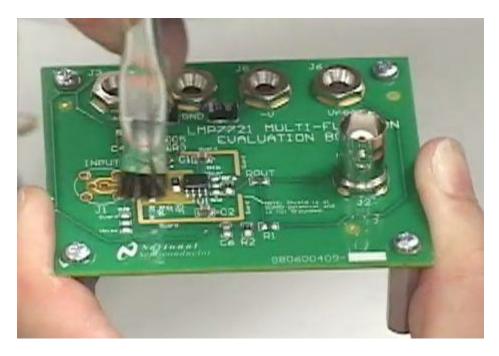

The setup was enclosed in a steel coffee can, covered with a metal lid or aluminum foil (not the plastic lid).

Figure 8: Test Circuit inside Coffee Can. (Test wire can be seen going to the input)

A long, thin piece of grounded, un-insulated bus wire is run through a small hole in the top and inserted into the input. This wire can be seen in left side Figure 8. The end of the wire has been bent into a narrow "V" and friction-fit into the input pad so it will come out quickly and easily.

To start the test, the wire is pulled all the way out of the enclosure to open the input and begin the test. The output voltage is recorded at 10 second intervals for 500 seconds.

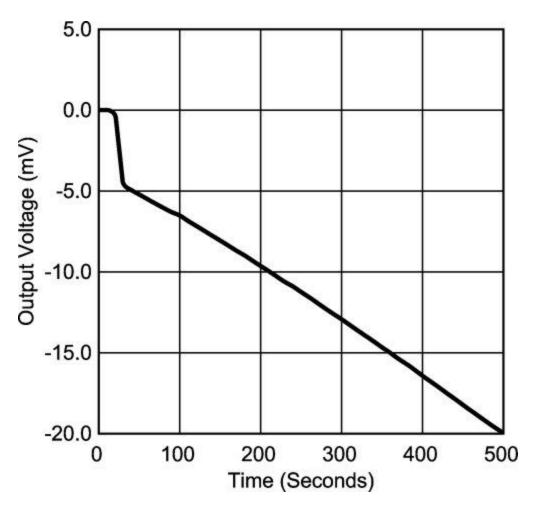

**Figure 9: Measured Open-Input Results**

Figure 9 shows the results. The wire was pulled out after the first two samples (20 seconds). Visible is the initial jump in the output after the wire was pulled out (due to mechanical disturbances). After about 40 seconds, the output settles to a constant drift rate of less than 1mV per second.

Using the known input capacitance (previously measured at about 12pF for this board), and the measured change in voltage and time, the input leakage currents can be calculated by integrating the output voltage over time using the simple formula:

$i = (\Delta v / \Delta t) * C$

Looking at Figure 9, we can make a rough calculation of the average input current. The output went from -10mV at 200 seconds, to -20mV at 500 seconds. The  $\Delta V$  is -10mV, and the  $\Delta T$  is 300 seconds. Inserting these values into the formula gives us about a femtoamp of leakage.

(-10mV/300sec) \* 12.2pF = -1.2fA

This is very good performance for an FR4 board!

### Measuring the Input Capacitance

### Measuring the Input Capacitance

The input capacitance is affected by several factors. Most prominent is the input capacitance of the amplifier and the trace capacitance.

Most op amps have input capacitances in the range of 2pF to 15pF, and as high as 40pF for "low noise" CMOS devices. Sockets, PCB traces, protection components, feedback elements, connectors and cables can add significantly to this value. The actual total capacitance value will dependent on your individual circuit and the layout.

Knowing the input capacitance of your circuit is critical to both the circuit design and the current measurement. There are various ways to measure the capacitance, such as using a capacitance meter, but there are problems with that approach.

Most capacitance meters are based on a "bridge" or AC source-measure configuration and cannot have one of their terminals grounded. Some handheld DMM's have capacitance functions, and you can take advantage of the "floating" aspect of the handheld device, but these meters are generally inaccurate in the picofarad range and/or are susceptible to noise pickup or proximity effects while "floating."

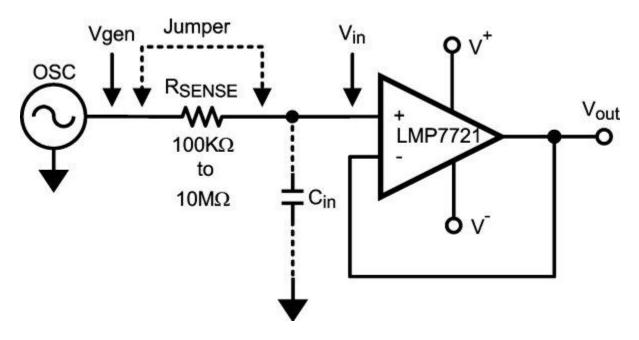

A simple technique involves using a large series value resistor (100K to >10M) added in series with the input and a sinewave signal generator (10Hz to ~100KHz).

Figure 10: Input Capacitance Test Circuit

An RC pole is created by the large series test resistor (Rsense) and the input capacitance (Cin).

To find this pole, an AC signal is fed through the series resistor while the generator frequency is swept until the monitored output amplitude drops to 70.7% of the reference frequency amplitude (-3dB). By knowing the pole frequency and resistor value, the input capacitance can then be calculated.

To perform the test, a temporary jumper is placed across the sense resistor to short it out. The scope or AC voltmeter is connected to the amplifier output (Vout) and the generator is then set to a low reference frequency; say 10Hz, and the amplitude set to some convenient value, like 100mV (Vgen).

The jumper across the test resistor is removed and the generator frequency is swept up until the output voltage drops to 70.7% of the initial Vin (70.7mV), and the generator frequency is noted.

The frequency and the resistance are now known, so the capacitance can now be calculated from the RC formula:

Cin = 1 / (6.28 \* R \* F)

For example, using a 10Mohm series resistor, we find that the 100mV output drops to 70.7mV at 1.305kHz. So:

Cin = 1 / (6.28 \* 10M \* 1305)

Cin = 12.2pF

There are a few points to be aware of with this measurement. The first is the stray capacitance across the sense resistor, generally around 0.15pF to 0.3pF for 1/4-watt resistors, can affect the results. The way to avoid this problem is to use several lower value resistors in series to create one large sense resistor with low capacitance. Each resistor's stray capacitance appears as a series capacitance, so the more resistors used in series, the less the total series capacitance.

To do this, the resistors are soldered end-to-end and allowed to bow up into the air, keeping away from nearby objects to minimize stray capacitance. For this measurement, five  $2M\Omega$  resistors were soldered end-to-end. See Figure 3 in Part 2 for a photo of the actual resistor string used.

The second point is to be aware of is the overall bandwidth of your circuit and to watch out for output slew rate limiting. It is a good idea that when you find the pole frequency, that you short the sense resistor again and make sure the amplitude is the same as the original reference frequency (~100mV) to verify you have not run out of bandwidth or hit slew rate limiting.

If the amplitude is not the same, increase the value of the sense resistor or add a known capacitance across the input to lower the pole frequency (add 20pF, then subtract 20pF from the result). Any capacitor type can be used for this test, as leakage is not important. To prevent slew limiting, use the lowest amplitude possible to achieve good results.

### **Summary**

I hope this tutorial gives you a better understanding of the challenges involved with sub-picoamp measurements. Creativity is the best tool at these levels. As with any time you are pushing up against the limits of nature, be prepared for minor setbacks and circuit or layout revisions.

### **Recommended Resources and Reading**

Keithley Instruments, Inc. Low Level Measurements Handbook, 6th Edition. Cleveland, OH., 2004. Section 2 is of most general interest.

### References

[6] "Op Amp Eval Board Cleaning for Femtoampere Bias Currents," Texas Instruments Corporation website, online video now available at:

### Author's biography

S.E Nickols is the CTO/ Principle Engineer of Diablo Mountain Research, LLC.

| For More Information |                      |             |                  |

|----------------------|----------------------|-------------|------------------|

| Agilent Technologies | Keithley Instruments | Rogers Corp | <u>Trompeter</u> |